1、首先,打开Quartus II 应用程序,并选择创建新工程按钮。2、这一步骤不需要修改任何参数,直接下一步即可。

3、修改保存路径以及工程名称。

工程名称不能任意的命名,要和程序当中的实体名保持一致。4、然后选中加进去的文件名,点击下一步即可。5、这一步需要我们选择器件,在Family框中选择系列,或者具体选择一个器件。6、到了这工程就建好了,直接点击完成按钮就是了。

quartus ii和modelsim有什么区别?

一、性质不同:quartus ii:quartus ii是综合性PLD/FPGA开发软件。modelsim:modelsim是HDL语言仿真软件。

二、特点不同:1、quartus ii:支持包括原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

2、modelsim:提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核。扩展资料Maxplus II 作为Altera的上一代PLD设计软件,由于其出色的易用性而得到了广泛的应用。目前Altera已经停止了对Maxplus II 的更新支持,Quartus II 与之相比不仅仅是支持器件类型的丰富和图形界面的改变。

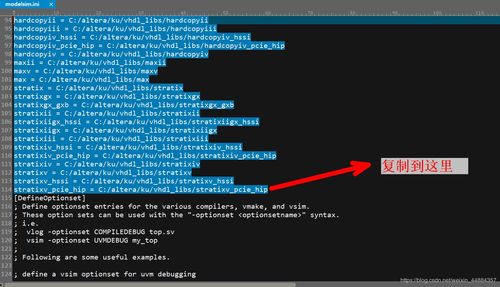

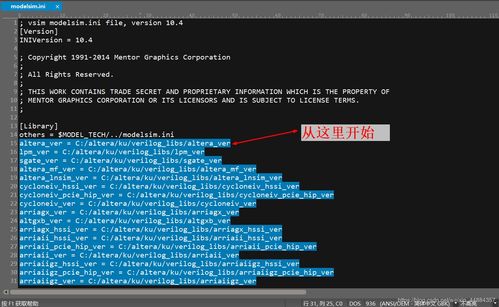

ModelSim有几种不同的版本:SE、PE、LE和OEM,其中SE是最高级的版本,而集成在 Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本。

如何使用quartus ii综合

QuartusII 是Altera公司开发的功能最强大的PLD编译工具,全面取代MAX+PLUS 使用步骤:一、建立工程. 1、「File」→「New Project Wizard」开始新工程的建立设置。『NEXT』 2、指定project的路径,和project的名称,顶层文件的名称(一般与工程名相同)。

3、指定project中要include 的文件。

4、选择project中要使用的一些EDA TOOLS。 5、选择所使用的器件的家族“family” 和具体型号。 6、『finish』 完成工程的设置。二、输入文件. 在工程中新建设计文件:图形文件“Block Diagram/Schematic File”,Verilog语言文 件“VerilogHDL File” 1、完成工程文件的输入,若为顶层文件,则文件名应该保存为与工程名相同。

2、编译设置:「Assignment」→「Compiler Settings Wizard」→「Next」 3、根据编译窗口的提示修改错误。 4、编译后会生成编译报告“Compilation Report”会分成如下几项: (1) Analysis&Synthesis语法检查,把大电路转成较小的元件 (2) Fitter 器件资源利用情况,引脚分配情况等 (3) Assembler 连线各元件 (4) Timing Analyzer 时间分析三、仿真. 完成工程文件的编译、综合、时间、分析后就可以建立波形仿真文件进行功能仿真 1、建立仿真文件 「File」→「New」→「Other Files」→「Vector Waveform File」→「OK」 2、选择输入输出引脚 Edit→「Insert Node or Bus」→「Node Finder」,在「Filter」处选择「Pins:all」,再按下「 >>」将所有选中的引脚添加到“Seleted Nodes”框,点「OK」→「OK」完成引脚添加。可通过右键 修改引脚的显示方式、属性、初始值等参数。

3、仿真时间、栅格的设置 Edit→『End Time』 设置仿真结束的时间, 『Grid Size』设置每个栅格表示的时间。仿真时间是 以建立仿真文件时给出的结束时间为准,仿真设置“Wizards”中设定的End Time没用。 4、仿真编译设置 『Assignments』→『Wizards』→『Simulator Settings Wizard』→选择当前要仿真得文件 仿真文件做好后还要将其设置为当前仿真文件,才可以开始仿真。

因为有时一个工程需要建立多个 仿真文件,这就需要通过设置确定仿哪个文件了。在选择仿真类型“Type of simulation”时,“ timing”代表考虑延时,“functional”表示功能型的仿真。 5、先编译后仿真 『Processing』→『Start Compilation&Simulation』 6、仿真结束后会生成仿真报告“Simulation Report” 仿真结果并不是出现 在所建立得仿真文件中,在仿真报告中有独立的仿真结果。

仿真的结果总是与当前的工程文件相对应,工程文件改变后要重新仿真后才有意义。四、将工程模块化,利用图形设计文件建立更大的工程 模块工程文件(“Block Diagram/Schematic File”或“Verilog HDL File”)编译仿真成功后就可以 将其模块化,然后在更高层次将各个模块级联起来,构成更大得工程。 1、模块化 『File』→『Creat/Updata』→『Creat Symbol Files for Current File』 然后编译器会自动将当前工程完整得编译一遍,然后生产图形模块,放在存放当前工程的文件夹里。 2、更大的工程 (1)建立工程文件 「File」→「New」→「Device Design Files」→「Block Diagram/Schematic File」→「OK」 (2)输入元件 右键→『Insert』→『Symbol』→可以在库文件中选,也可以通过“浏览”将已经建立图新模块的 工程加载进来。

标签: